منطق الباعث المقرنECL

منطق الباعث المقرن (بالإنجليزية: Emitter-coupled logic) عائلة منطقية فائقة السرعة، تستغل المقحل زوجي الأقطاب، وتكون في هيئة دارة متكاملة.

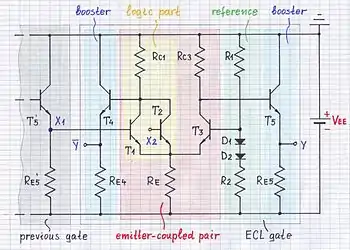

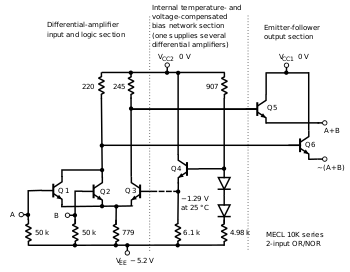

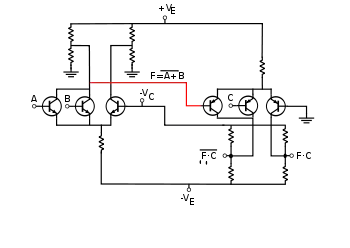

تبنى دارات في هذه العائلة على بوابات تستخدم ترانزيستورات لا تصل إلى الإشباع ولذلك فهي سريعة العمل.تستخدم عائلة ECL مصدر تغذية سالب وتستهلك قدرة كبيرة بالمقارنة مع باقي العائلات. البوابة الاساسية لهذه العائلة هي بوابة OR/NOR و البيئة الداخلية لهذه البوابة مبينة في الشكل في الاسفل(دائرة الاساسة ECL ) و تعتبر عائلة ECL من أكثر العائلات المنطقية تأثراُ بالضجيج الكهربائي . مخرج مرتفع 1 في هذه العائلة يقابل جهدا يتراوح بين (0.75_-0.8V) أما الصفر منطق 0 يقابل جهدا يتراوح بين (1.55- و 1.8- ) . وتستخدم الدارات المتكاملة من عائلة ECL في الاجهزة الخاصة مثل معالجات الشارة الرادارية والحواسيب ذات السرعات العالية.

تبنى دارات هذه العائلة على بوابات تستخدم ترانزيستورات لا تصل إلى الإشباع ولذلك فهي سريعة العمل

السلبية الاساسية في دوائر ECL انها تستهلك تيار عالي في كل ترانزيتسر موجود فيها هذا بدوره يأدي إلى زيادة استهلاك الطاقة

التغير في مسار الإشارة في ECL و تغير موقع المدخل يعرف باسم مشتقة تغير التيار DCS [2]

التاريخ

اخترع ECL في آب / أغسطس 1956 في IBM من قبل هانون يورك S. Yourke.[3][4] في الأصل كما أنها تستخدم تصنيع الدوائر الكهربائية في، IBM 7090و IBM 7094 أ.[5] و .[6] ASLT ا IBM 360/91.[7][8][9]

العملية

تسمى البوابة المعطاة في الشكل الذي في الاسفل بوابة OR/NOR و هي البوابة الاساسية في عائلة ECL و في هذه البوابة اما تكون الترانسيستورات في حالة التشغيل ON و تعمل في المنطقة الفعالة

أو تكون في حالة الإيقاف OFF . ولاتعمل الترانزيستورا نهائيا في منطقة الإشباع ولذلك تعتبر عائلة ECL اسرع من باقي العائلات المنطقية ولكنها تستهلك طاقة أكبر .

- ولكن عند وصول التغذية إلى دارة البوابة يكون T3 في حالة عمل ON و فيما يلي نتعرف على آلية العمل في الحالات المنطقية المختلفة لجهود المخل عندما تكون جهود المدخلين صفر منطق أي (-1.55) فان جهد نقطة التقاء بواعث T2 وT1 و الذي سنرمز له بالرمز VE سيكون VE=VBE+VB=-(1.15+0.75) و يساوي -1.9 و بما ان جهود قواعد T1 T3 هي -1.55 فان الفرق بين جهد القاعدة والباعث لهذه الترانزيستورات سيكون VB-VE =-1.55+1.9 =0.45 و هو اقل من 0.7 و تكون هذه الترانزيستورات في حالة قطع OFF . ,و في هذه الحالة لا يمر تيار عبر المقاومة R1 وجهد قاعدة T6 يساوي الصفر أما باعث الترانزيستور فموصول عبر مقاومة إلى جهد التغذية -5.2 فيكون الترانزيستور T6 في حالة ON والجهد على باعثه يساوي مرتفع VET6 =-0.75 ويعتبر هذا الخرج هو الخرج NOR للبوابة .يؤدي مرور تيار عبر المقاومة R2 بسبب كون الترازيستور T3 في حالة ON إلى تشكيل جهد يساوي -0.8 على قاعدة T5 و يكون جهد باعث T5 مساويا VET5=-0.8-0.75=-1.55 LOWويعتبر باعث T5 هو الخرج OR للبوابة.

الخصائص

تعتبر دوائر ECL ذات ضوضاء منخفض من حيث الطاقة ويعزى ذلك انه التيار المطلوب لعمل الدائرة عالي ولكنه ثابت .على غرار دوائرة منطقية اخرى التي يكون فيها ضوضاء الطاقة عالي بسبب حالة الانتقال المتكرر

وقت النتشار يكون اقل الف مليون جزء من الثانية نانوا سيكند وهو بذلك يعتبر من اسرع العوائل الالكترونية .[11][12]

و قاموا بتطوير ECL مع الزمن ومثال على ذلك من عام 1975-1991 قامة شركة Digital Equipment Corporation's بتصنيع from the (ECL) KL10 through the (ECL) VAX 9000 until the 1991 single-chip CMOS NVAX. كان معكم احمد وليد الشريف 0116032

مراجع

- Original drawing based on William R. Blood Jr. (1972).

- E. B. Eichelberger and S. E. Bello (May 1991). "Differential Current Switch – High performance at low power". IBM Journal of Research and Development. 35 (3): 313–320. doi:10.1147/rd.353.0313. مؤرشف من الأصل في 03 مارس 2016. الوسيط

|CitationClass=تم تجاهله (مساعدة) - في Early Transistor History at IBM نسخة محفوظة 24 يونيو 2017 على موقع واي باك مشين.

- Yourke, Hannon S. (October 1956), Millimicrosecond non-saturating transistor switching circuits (PDF), Stretch Circuit Memo # 3 الوسيط

|CitationClass=تم تجاهله (مساعدة); الوسيط|separator=تم تجاهله (مساعدة)CS1 maint: ref=harv (link). - E. J. Rymaszewski; et al. (1981). "Semiconductor Logic Technology in IBM" (PDF). IBM Journal of Research and Development. 25 (5): 607–608. doi:10.1147/rd.255.0603. ISSN 0018-8646. مؤرشف من الأصل (PDF) في 20 مارس 2009. اطلع عليه بتاريخ 27 أغسطس 2007. الوسيط

|CitationClass=تم تجاهله (مساعدة) - Thorpe, Darrell, المحرر (1963). High-Speed Switching Transistor Handbook. Motorola. مؤرشف من الأصل في 14 ديسمبر 2019. الوسيط

|CitationClass=تم تجاهله (مساعدة); الوسيط|last1=مفقود في editor (مساعدة)CS1 maint: ref=harv (link) - IBM's 360 and Early 370 Systems. 2003. صفحة 108. ISBN 0262517205. الوسيط

|CitationClass=تم تجاهله (مساعدة) - J. L. Langdon, E. J. VanDerveer (1967). "Design of a High-Speed Transistor for the ASLT Current Switch" (PDF). IBM Journal of Research and Development. 11: 69. doi:10.1147/rd.111.0069. مؤرشف من الأصل (PDF) في 26 أبريل 2020. اطلع عليه بتاريخ أغسطس 2020. الوسيط

|CitationClass=تم تجاهله (مساعدة); تحقق من التاريخ في:|تاريخ الوصول=(مساعدة) - "Logic Blocks Automated Logic Diagrams SLT, SLD, ASLT, MST" (PDF). IBM. صفحة 1-10. مؤرشف من الأصل (PDF) في 08 مايو 2018. اطلع عليه بتاريخ 11 سبتمبر 2015. الوسيط

|CitationClass=تم تجاهله (مساعدة); تحقق من التاريخ في:|تاريخ أرشيف=(مساعدة) - Blood, W.R. (1972).

- John F. Wakerly.

- Sedra; Smith.

- بوابة كهرباء

- بوابة إلكترونيات

صور وملفات صوتية من كومنز

صور وملفات صوتية من كومنز