باور5

باور5 هو معالج دقيق من تصميم وصناعة شركة آي بي إم.[1] وهو من نوع معالجات سيمد التي تنفذ نفس التعليمة في نفس الوقت لكن مع معطيات مختلفة. يعمل هذا المعالج بتردد حوالي 1.5 إلى 2.2 جيجا هرتز. وليست له ميزات حقيقية سوى أن التردد فيه ممكن أن يرتفع قليلا أثناء فترة عمله.

| باور5 وحدة المعالجة المركزية | |

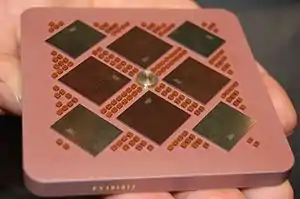

مجموعة متعددة الشريحة (بالإنجليزية: Multi-Chip Module) بأربعة معالجات باور5 | |

| أُنتج: | 2004 |

| المصنّع: | آي بي إم |

| أقصى و م م معدل: | 1.5 جيجا هيرتز/GHz إلى 2.2 جيجا هيرتز/GHz |

| أصغر حجم: | 130nm إلى 90nm |

| قلوب: | 2 |

| ذاكرة مخبأة: | 36 |

الشريحة الأولى

الخابيات

أنماطها:

- خابية التعليمات ذات المستوى الأول، ويبلغ حجمها 64 كيلوبايت، وهي من نمط عنونة مباشرة

- خابية المعطيات ذات المستوى الأول، وحجمها 32 كيلوبايت

وهي خابية تجميعية بمجموعات رباعية أي 4-way set associative 1.875 - وتحوي الرقاقة أيضاً خابية بمستوى ثانٍ يبلغ حجمها، والتي هي بدورها مقسمة لثلاثة وحدات كل منها بحجم 0.625 ميجابايت 10-way set associative ومن نمط خابيات تجميعية بمجموعات عشرية أي وأما خابية المستوى الثالث فهي بحجم 36 ميجابايت ومن نمط خابية تجميعية بمجموعات ثنائي عشرية أي 12-way set associative. تشكيلها: إن وحدات خابية المستوى الثاني متصلين بالمعالجات عن طريق قاطعة وحدة الواجهة الرئيسية (بالإنجليزية: CIU) 40 B/cycle) هي ذات الأبعاد 3*2 وبعرض نطاق ترددي يبلغ crossbar إن العارضة المشكلة لهذه القاطعة أي ال ( أي 40 بايت بالدورة الواحدة لكل نافذة. وهذا ما يمكن من نقل 32 بت بنفس الوقت. 8 B حتى من خابية التعليمات ذات المستوى الأول أو خابية المعطيات لكل من المعالجات وأن تخزن بقيم

وحدات أخرى

- كما ويوجد وحدة لكل معالج تسمى a Non-cacheable Unit والتي تشكل الواجهة مع متحكم البناء (بالإنجليزية: Fabric Controller) ويهتم أيضاً بالعمليات التي لا تحتاج لذاكرة خابية (بالإنجليزية: non-cacheable operations).

- وحدة البناء (بالإنجليزية: )Fabric Controller: هي المسؤولة عن الاتصال مع الرقاقات الثلاث الأخرى المضمنة في نفس وحدة الرقاقة المتعددة (بالإنجليزية: Multi Chip Module (MCM)) إلى خابية المستوى الثالث وإلى غيرها من الوحدات.

إن عرض الموجات هنا هو 1.9 غيغاهرتز هي 19.8 ، 13.2 ، و9.9 جيجابايت / ثانية ، على التوالي.

الشريحة الثانية

الخابيات

إن خابيتي المستوى الثاني لرقاقتين متجاورتين تكونا متصلتين، وخابيتا المستوى الثالث تكونا متصلتين بشكل مباشر مع خابيتي المستوى الثاني. إن خابيتي المستوى الثالث مقسمة أيضاً لثلاثة أجزاء وكل منها بمثابة خابية متدفقة (بالإنجليزية: Spill cache) لنظيرتها من المستوى الثاني. بمعنى أن المعطيات التي يجب أن تخرج من خابية المستوى الثاني تنقل إلى الجزء المقابل من خابية المستوى الثالث. إن خابية المستوى الثالث لها كمون من 80 دورة على عكس الذاكرة الرئيسية التي تملك كموناً 220 دورة. إن أفضل خصائص الذاكرة المخبئية أن تقود إلى أقل فترة انتظار وصول إلى المعطيات العادية. تقييم الترتيب العالي لمتعدد الحدود ولضرب مصفوفتين يحقق 90% أو أفضل من ذروة سرعة الأداء بينما تكون هذه من %75- 65 .POWER 4برقاقة المعالج

وحدات أخرى

إن الشريحة الأخرى لا تزال تحتوي على مجموعة متنوعة من الأجهزة:

- دليل خابية المستوى الثالث (بالإنجليزية: L3 cache directory)

- متحكم الذاكرة (بالإنجليزية: Memory Controller) والذي ينبغي أن تخفض الكون خارج الشريحة إلى حد كبير.

- متحكم الرسوميات (بالإنجليزية: GX Controller) المسؤول عن الحركة على مسار الرسوميات (بالإنجليزية: GX bus)، هذا المسار ينقل المعطيات من وإلى النظام، وفي يستخدم عملياً للإدخال/والإخراج أو شبكة اتصالات سريعة.

أنه لا يساعد في الوصول للمعطيات بشكل نظامي،POWER 5+ هناك ميزة أخرى لل لكنه ممكن أن يكون ذو فائدة بالنسبة للبرامج التي يكون الوصول فيها للمعطيات ليس نظاميا كثيراً.

خاصية المعالجة المتعددة (بالإنجليزية: Simultaneous Multithreading (SMT)): إن معالجات الباور5 قادرة على تشغيل عمليتي معالجة تعملان بنفس الوقت.

باور5 وباور3

في كثير من الأحيان تكون نواة باور5 مشابهة للمعالج باور3. فهناك: وحدتان وظيفيتان حقيقيتان بدلاً من ثلاث والتي تسمى Fixed Point Unit وبدلاً من وحدة تفرع وإرسال مدمجة، تحتوي نواة باور5 على وحدة تفرع وتسجيل شرطي منفصل، كما وتملك 8 وحدات تنفيذ. إن لوحدة التنفيذ مجموعة تعليمات مرتبطة بها تمكنها من الخروج عن ترتيب المعالجة (التفرع) تصل إلى 200 تعليمة بمراحل مختلفة. إن وجود العديد من التعليمات بوقت واحد يتطلب وجود معدات للتنبؤ متطورة للغاية. على عكس المعالج باور3 فإن بنية باور5 تنفذ وحدات الفاصلة الثابتة العمليات الحسابية الحقيقة التي يمكن أن تنتهي بدورة واحدة وكذلك العمليات المتعددة الأدوار كالضرب والقسمة الحقيقيين. لا يوجد وحدات فاصلة عائمة منفصلة للعمليات التي تتطلب أكثر من دورة كالقسمة وإيجاد الجذر التربيعي (كل عمليات الفاصلة العائمة تنفذ في وحدات الفاصلة العائمة).

على الرغم من وجود معالج ثنائي اللب من باور5 إلا أن الإصدار الأحادي القناة يتم تسويقه على أنه فعال الاستخدام بالحواسيب العالية الأداء (بالإنجليزية: HPC). والسبب أنه في هذه الحالة يكون عرض نطاق الحزمة بخابية المستوى الثاني من غير الضروري أن يكون مشتركاً بين ممكن التحقق .108.8 GB/s المعالجات والنقل الحر يصل إلى 163.2 GB/s تكون ذروة النطاق الترددي Dual coreبينما بالإصدار ذو القناتين أي ال وعليه يجب أن يكون مشتركاً بين كل معالجين .

انظر أيضاً

مراجع

وصلات خارجية

- بوابة إلكترونيات

- بوابة تقنية المعلومات

- بوابة علم الحاسوب

- بوابة كهرباء